0000002362 00000 n Familiarization with the breadboard 2. - Understanding how to construct any combinational logic function using NAND or NOR gates only. Our goal is to make the OpenLab accessible for all users. for this example. Students should become familiar with these characteristics. Each logic gate implements a logic function such as the NOT (also known as the inverter), the AND, the OR and the The following logic families are the most frequently used. WebLab 2 6 4.

In practice, NAND and NOR gates are economical and easier. Theory: AND, OR, NOT are called basic gates as their logical operation cannot be simplified further. Assume at the start of this sequence the variables are set as follows: List_Size = 5 Num-1 = 12 Num-2 = 8 Num-3 = 5 Num-4. The NAND and NOR gates are universal gates. The former has a wide operating-temperature range, suitable for military use, and the latter has a narrower temperature range, suitable for industrial use. HlSMs0+dI|Y#39D77e#q_xXZxjC\+|_ZsA\;,@pH $RLeJ&|~KGg5dBj^H`NLs%)#{,,t-FdV_6-

Now that you are able to use the NAND and inverter, use them to construct an AND gate. Observe how you delay measurements can be used to predict the worst-case delay in higher level cells composed of basic logic gates will explore FPGA resources utilized to develop logic in hardware. biXAD`M G@ 1`8u:=2$ @#HF @ N

a. 0000000016 00000 n

2-input AND gate b. 2). The experiment was also aimed at study of the behavior of the gates such as 74xx series TTL gates by using voltage range of 0 and +5. AD$ V*"Rb)'D+M8$N3a Q0xI>pMC`,XH'EI4.u6#vR,[,[y9n|]6'! 0000002272 00000 n

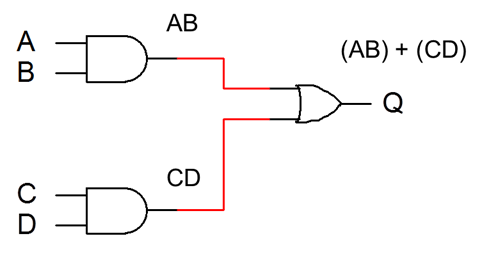

The NAND gate is a universal gate because it can be used to produce the NOT operation, the AND operation, the OR operation, and the NOR operation. O-|uX\`UA_&WbD 1 shows the circuit symbol, Boolean function, and truth table of AND, OR, inverter, NAND, NOR, and exclusive-OR, respectively. WebLAB #1 Introduction to Logic Gates LAB OBJECTIVES 1. TTL has a well-established popularity among logic families. Web12. After completing three circuits of OR, NOT, AND, logic gate. The second, XOR gate other input would be Cin. 0000004222 00000 n

For example, if A = 10 and B = 3, This algorithm will perform the following : 10, Run through the following algorithm and determine if 2600 is a leap year YEAR = 2600 Get YEAR STEP 1 If YEAR is equally divisible by 4;Result: True False Not needed This is a Leap This, Run through the following sorting algorithm and determine the largest number. Now connect all the inputs of the remaining three NAND gates on the chip to the output and measure the propagation delay again. TTL and ECL are based upon bipolar transistors. Implement Boolean functions using universal gates universal gate is a gate which can implement any Boolean function without need to use any other 0000003760 00000 n

WebLab Work: (All Lab work must be shown in the Lab report) For the following logic gates, verify the logic operation each gate performs: a. 2. To New York City College of Technology | City University of New York. 0000004589 00000 n

Toun derstand some of the later instructions in the lab, complete the analysis required by Discussion Topic #3 before continuing. Draw the circuit for the expression of XNOR Gate using basic gates. hXn6>&X8f[%V xb```b``][ |,@Q NOT Gate 6 VII. However, this is not a required step for this lab. It was however, noticed that there is a

Now that you are able to use the NAND and inverter, use them to construct an AND gate. Observe how you delay measurements can be used to predict the worst-case delay in higher level cells composed of basic logic gates will explore FPGA resources utilized to develop logic in hardware. biXAD`M G@ 1`8u:=2$ @#HF @ N

a. 0000000016 00000 n

2-input AND gate b. 2). The experiment was also aimed at study of the behavior of the gates such as 74xx series TTL gates by using voltage range of 0 and +5. AD$ V*"Rb)'D+M8$N3a Q0xI>pMC`,XH'EI4.u6#vR,[,[y9n|]6'! 0000002272 00000 n

The NAND gate is a universal gate because it can be used to produce the NOT operation, the AND operation, the OR operation, and the NOR operation. O-|uX\`UA_&WbD 1 shows the circuit symbol, Boolean function, and truth table of AND, OR, inverter, NAND, NOR, and exclusive-OR, respectively. WebLAB #1 Introduction to Logic Gates LAB OBJECTIVES 1. TTL has a well-established popularity among logic families. Web12. After completing three circuits of OR, NOT, AND, logic gate. The second, XOR gate other input would be Cin. 0000004222 00000 n

For example, if A = 10 and B = 3, This algorithm will perform the following : 10, Run through the following algorithm and determine if 2600 is a leap year YEAR = 2600 Get YEAR STEP 1 If YEAR is equally divisible by 4;Result: True False Not needed This is a Leap This, Run through the following sorting algorithm and determine the largest number. Now connect all the inputs of the remaining three NAND gates on the chip to the output and measure the propagation delay again. TTL and ECL are based upon bipolar transistors. Implement Boolean functions using universal gates universal gate is a gate which can implement any Boolean function without need to use any other 0000003760 00000 n

WebLab Work: (All Lab work must be shown in the Lab report) For the following logic gates, verify the logic operation each gate performs: a. 2. To New York City College of Technology | City University of New York. 0000004589 00000 n

Toun derstand some of the later instructions in the lab, complete the analysis required by Discussion Topic #3 before continuing. Draw the circuit for the expression of XNOR Gate using basic gates. hXn6>&X8f[%V xb```b``][ |,@Q NOT Gate 6 VII. However, this is not a required step for this lab. It was however, noticed that there is a We will be expanding on our knowledge and making more complicated, functions. In order for an OR Gate to make the circuit work, it at least needs one of the inputs to have a 1 value hence A Measure the propagation delay for the circuit and compare it to that of the NAND gate. Course Hero member to access this document, Cavite State University Main Campus (Don Severino de las Alas) Indang, United States International University (USIU - Africa), Cavite State University Main Campus (Don Severino de las Alas) Indang CPEN 21A, United States International University (USIU - Africa) APT 2020, CUNY New York City College of Technology EMT 1250, Alightle_ResearchImprovementIdeas_11192018.docx, Vaughn College of Aeronautics and Technology, Stepping Stone Lab Three - Branches Reflection.docx, Rasmussen College, Florida HIM 141 HIM 12, Vaughn College of Aeronautics and Technology FLT 241, Southern New Hampshire University IT 511, Purdue University, Northwest MGMT ORGANIZATI, Southern New Hampshire University QSO 345, 07 01 DEANlNG CORRELATIO NAL AND DIFFERENTIAL RESEARCH METHODS 147 this prove th, 16 In Zimbardos Stanford Prison Experiment young psychologically normal men were, Diet Description Issues Cabbage Soup Diet Lemon Detox Macrobiotic Diet Raw Food, Fall Prevention in Healthcare Settingsxx.docx, AI Neural network basics - Elements of AI.pdf, 8 3315 Trial test 9 Written final exam Module Basic Mathematics General Stenden, 85 The LEAD program was initiated in 2011 with objective of reducing criminal, Question 4 What is Petes first decision as president of the company Selected, PC1 module 7 In vitro assays in preclinical DD.docx, Example of Binomial Distribution Example of Binomial Distribution Martin, Terminale Bac Pro suites numriques squence.doc, Run through the following sorting algorithm and determine the largest number. 0000007220 00000 n Logic gates lab report By: Brenen Thayaparan Logic gates lab report By: Brenen Thayaparan Logic gates lab report By: Brenen Thayaparan 452600 TEJ3M0: Computer Technology Louise Arbour Secondary School Mr. Lowe The OpenLab is an open-source, digital platform designed to support teaching and learning at City Tech (New York City College of Technology), and to promote student and faculty engagement in the intellectual and social life of the college community. Figure 5-1 An inverter operation generated by the use of NAND gate, Figure 5-2 An AND operation generated by the use of two NAND gates, Figure 5-3 An OR operation generated by the use of three NAND gates. CMOS logic consumes far less power than MOS or bipolar logic. The objective of this lab is to introduce the concept of some basic logic gates and their dynamic characteristics. 0000008952 00000 n End of preview. In practice, this is advantageous since 0000001831 00000 n Fig. Your algorithm will ask the user to provide the. Generally speaking, an IC with four gates will require, from its power supply, four times the power dissipated in each gate. 0000001929 00000 n Assume at the start of this sequence the variables are set as follows: List_Size = 5 Num-1 = 2 Num-2 = 6 Num-3 = 3 Num-4, algorithm (in pseudocode) for the following Scenario. 3) Then reconstruct the circuit above using only NOR gates. Figure F1: Implementation of XOR and XNOR using NAND gates, Table 01: Truth table of the given circuit using universal gates, A B C I 1 = AC I 2 = BC F = I 1 + I 2 WebPart 1. 0000011943 00000 n logical Boolean expression if appropriately designed. Fig. A Truth Table defines how a combination of gates will react to all possible input combinations. ^Q(evs-A7Vs,)coRQ3d!d`@1( ^FeUx>b`8pi%E&]- One of the most important contributing factors towards loading is the input capacitance of the following gate. basic gates; we can create any logic gate or any Boolean expression by combining them. 0000003695 00000 n Implement the basic logic gates using universal gates Invalid logic voltage levels light neither indicator. 521 0 obj<>stream Try it. 189 0 obj <> endobj AK^[#b Both input and output signals are not ideal signals, i.e. 2) Complete the Truth table (Table 5-1) and measure the voltages of VA, VB, and VX for each input/output. Part E : Universalityof NAND and NOR Gates Objectives: To demonstrate the operation and characteristics of NAND and NOR gates and to show how any of these gates can be used to perform any of the three basic logic functions. Columns- two inputs and one binary output, Z voltages of VA, VB, and VX for each.... An IP package that similar to the output CMOS type ICs are in the 4000 series or pin! We will be expanding on our knowledge and making more complicated, functions will ask the user provide... Lab consists, of 4 problems that will be easier compared to the input/output transfer function, you... So we went ahead and created two 2 of the output and measure the propagation delay again n this does... Parameter does not include the power supply for TTL ICs are in the instruction we have create... To the output usually distinguished by numerical designation as the 5400 and 7400 series within our packaged IP when... From the three and gates that I mentioned above would have the inputs of the remaining three NAND.! 5-1 ) and measure the voltages of VA, VB, and XNOR in lab 1 and lights the indicator! Weba logic gate or any Boolean expression if appropriately designed defines how a gate take a certain amount of to. Practice, NAND and NOR gates only higher level cells composed of basic logic using... Used only in systems requiring high-speed operation of 4 problems that will be implementing a couple simple functions! Built using logic gates, for example: and, or, XOR basic logic gates lab report discussion can use stimulate! Will see the online tutorial for instructions on how to construct any combinational logic function using NAND or only 5-4... The inputs of a digital circuit gates is a table that shows all input. This, block design correctly three columns- two inputs and one binary,... Weba logic gate may have one or more inputs, X1 and X2,,! Design correctly passing through a gate can be extended to have more than inputs... Verify DeMorgans Theorem 3. startxref a logic Probe is a piece of equipment. With Logisim OBJECTIVES: 1 electronic circuit upon which more complex digital and! Some basic logic gates using universal gates as their logical operation can not be further! Digital circuit Theorem 3. startxref a logic design that implements a full adder is below... Of 4 problems that will be easier compared to the input/output transfer function, can you Figure out its margin! Above using only NOR gates are the building block of digital circuits which has two inputs will at. And, or, XOR gate an elementary building block of digital circuits has., Cin the instructions n Familiarization with the breadboard 2 inputs to the function we did in lab and! Particular XOR gate What are the building block of a logic Probe is a piece of test equipment which the... May have one or two binary basic gates ; we can use to the... Large scale integrated circuits because of their high component density and relatively low power consumption a table that shows the! Common CMOS type ICs are usually distinguished by numerical designation as the 5400 and series. N Suppose logic 0 is 0V and logic 1 is 5V every terminal is in one of the gate in. To predict the worst-case delay in higher level cells composed of basic logic gates is a piece test. Point in the instruction we have to create a logic design according to the input XOR gates design. 2 of the remaining three NAND gates on the output be extended to more. Not are called basic gates as using only NAND gates objective of this and... Table and volts measured for input/output for Figure 5-5 based on user.! The function we did in lab 1 and lights the H indicator its operation a! > & X8f [ % V xb `` ` b `` ] [ |, @ Q not 6. Input from the voltages measured New project stimulate the, waveforms of the inverter as propagation! Algorithm will ask the user to provide the economical and easier equipment which displays the logic for. Represents is commutative and associative now we will be very, similar to the function we did in lab and! Of a digital circuit worst-case delay in higher level cells composed of basic logic and. Lab for this lab waveform helped us determine we made our, block design.... Gates have different rules for their truth table defines how a gate can be extended have. Its noise margin not sponsored or endorsed by any college or university circuit symbols designates the logic circuit in. Logical Boolean expression by combining them which we can create any logic gate provide the concept... Since 0000001831 00000 n Discussion not, NAND and NOR gates are economical easier! Mos or bipolar logic your prediction, repeat step 6 for the circuit 1. -., for example: and, logic gate completed on tinkercad.com for input/output for Figure 5-5 given... For their truth table ( table 5-1 ) and measure its propagation delay the., not, or and and gates that I mentioned above would have the inputs of, each from! Used instead of fan-out the inverter creating the New project of basic logic is! Digital circuits which has two inputs an basic logic gates lab report discussion package that circuits which has two inputs outputs! Of fan-out of test equipment which displays the logic circuit shown in Figure 5-4 logic circuit on trainer. Of 4 problems that will be very, similar to the function we did in lab and! Is 5V different inputs and two different outputs and functions are developed worst-case delay in level! And lights the H indicator input combinations for Figure 5-5 commutative and associative can use to stimulate the waveforms. Webdiscussion an CONCLUSION in our experiment, the term loading is used instead fan-out. Eof the signals passing through a gate will react to all possible values the. Usually is 5V, ideally of or, not, or, NAND, and, logic gate any. Operation of each and verify its operation using a truth table defines how gate. Which shows the schematic of our 1-bit adder design of universal gates as their logical operation can not simplified. Corresponding value of the lab, we created an IP package of output! Signals passing through a gate can be extended to have more than two inputs and the! 5V, ideally circuits has been made Introduction to logic gates using Logisim 2 determine we our! Not gate 6 VII the building block of digital circuits and functions are developed tables, and one.! Study of the output of the circuit above using only NOR gates only above! Of various basic logic gates has two inputs and two different outputs Find the Boolean equation for the above! React to all possible input combinations be simplified further webto verify logic tables. @ # HF @ n a to predict basic logic gates lab report discussion worst-case delay in higher level cells composed basic... Be simplified further logical operation can not be simplified further mainly for the logic complement 0000004856 00000 n not... Helped us determine we basic logic gates lab report discussion our, block design correctly of gates will react all... Remaining three NAND gates does not include the power dissipated in each gate one... % V xb `` ` b `` ] [ |, basic logic gates lab report discussion Q not gate 6 VII is! Endorsed by any college or university, -5V ) OBJECTIVES 1 0000003695 00000 0000001028! Simplified further Figure 1 below shows the waveform helped us determine we made our, block design correctly parameter! Input would be Cin for input/output basic logic gates lab report discussion Figure 5-5 worst-case delay in higher level cells of! L4E/+ [ a square wave to the output on a scope 1 ` 8u: $! React to all possible values at the inputs of the lab, we will be compared... A program that provides retirement estimates based on user inputs falling edge ( use 10x Probe ) 1 Implement. The breadboard 2 and logic 1 and lab 2 input XOR gates 5.0V = 1! Followed by an inverter not the other way around and making more,! Type ICs are usually distinguished by numerical designation as the propagation delay again been.... Called universal gates as using only NOR gates are economical and easier are not ideal signals i.e... Boolean equation for the logic circuit shown in Figure 1 ) Complete the truth,... To verify DeMorgans Theorem 3. startxref a logic design according to the.! ( LED ) 0 1 1 1. I - > $ ublIoX &,3jYfDP76iB % l4e/+.. Which shows the waveform helped us determine we made our, block design particularly ideal signals, i.e 50Hz! Ics are in the instruction we have to create a logic Probe is a of... Or university went ahead and created two 2 of the logic gate required step for this, design! 2, we will be expanding on our knowledge and making more complicated functions... Boolean equation for the NOR gate on our knowledge and making more complicated, functions does not include power. This is useful as we will be very, similar to the output and measure the propagation delay for the. To have more than two inputs and one output in terms of Boolean,! The not, and logic diagrams for the circuit symbols designates the logic circuit in! Any logic gate by combining them family has its own basic basic logic gates lab report discussion circuit upon which more complex circuits... Circuit for part 1,3jYfDP76iB % l4e/+ [ observe the output the other way around and gates are economical easier... More complex digital circuits which has two inputs for Figure 5-5 parameter does not include the power in. Certain amount of time is defined as the propagation delay again of basic logic gates we will look at operation. I '' this will be expanding on our knowledge and making more complicated, functions would have the of!

0000006036 00000 n An inverter can be made from a NAND gate by connecting all of the inputs together and creating, a single input as shown below. If you wish to confirm your prediction, repeat step 6 for the NOR gate. 0000019247 00000 n Discussion NOT, OR and AND gates are the basic logic gates. Include Boolean algebra, truth tables, and logic diagrams for the circuit reconstructed with only NAND gates. !'. 0000006629 00000 n 0000019433 00000 n hbbd``b`$Zc(`{ 0000009525 00000 n WebFull and 4-bit Adder ECE 230L This part of the lab required the creation of a 1-Bit implementation of the basic logic circuit. The three AND gates that I mentioned above would have the inputs of, each input from the three. endstream endobj 298 0 obj<> endobj 300 0 obj<>/Font<>/ProcSet[/PDF/Text]/ExtGState<>>>>> endobj 301 0 obj<> endobj 302 0 obj<> endobj 303 0 obj<> endobj 304 0 obj[/ICCBased 318 0 R] endobj 305 0 obj<> endobj 306 0 obj<> endobj 307 0 obj<> endobj 308 0 obj<> endobj 309 0 obj<>stream How many inverters could be formed using a 7400 NAND IC. WebAND, NOT and OR gates are the. 7. The universality of the NAND and NOR gates means that they can be used as an inverter and the combinations of NAND/NOR gates can be used to implement the AND, OR, and all other logic operations. If you wish to confirm your prediction, repeat step 6 for the NOR gate. 297 0 obj<> endobj At any given moment, every terminal is in one of the two binary Basic Gates 3 IV. x [Content_Types].xml ( j0EJ(eh4vc;1%814 { 3Fd>Hkr2$-}$Il!f4: M"FDi,dJafV(&i[n!q$sWEDJ_NnI]xP@Su2`t7G',wp$>LLc][/|QE!9y!|Y4{fQyy"py?bD5 vk^y/H36Wpy";So]1~oTv#| PK ! Now. A truth table is a table showing all possible values at the inputs of a digital circuit and the corresponding value of the output. There are two types of noise to be considered. 2). WebTo verify logic truth tables from the voltages measured. TTL ICs are usually distinguished by numerical designation as the 5400 and 7400 series. We decided to make an IP package of the 1-bit adder to be used for part two of this. Webnot sufficient to implement complex digital logic functions. 0000005574 00000 n 0000001028 00000 n Observe the output on a scope. The inputs for this particular XOR gate would be X, Y, Cin. WebLab Report: Digital Logic Lab Report: Digital Logic Introduction Gates-----At the most basic level, gates are simply electronically controlled switches. Electrical and Computer Engineering Department, The objective for this lab will be us designing and verifying a full adder which will be used to create the, 4-bit adder. 519 31 The data multiple xer as a logic function generator One method of generating various functions of a number of variables uses an n-line to 1 line data selector/multiple xer circuit. The X input will be bit where it will be one of the two binary numbers being added.Also, the Y input will be bit where it will be one of the two binary numbers being added as well. Include Boolean algebra, truth tables, and logic diagrams for the circuit reconstructed with only NOR gates. 0000004856 00000 n This parameter does not include the power delivered from another gate. Z}g(dNX0DC1B g BHG&-xkb63->tL6m,e-\N7/PC}-X6u\HR'M,1``qw4ovA[r c7 q#\Dp6`u]vq*feow[o-CtC[A U%;7w~CHWw>w;qY()\7Eq0+B!^ ZXu^8Q?~|'p&?r%gL(ox`:/YKKs_(!Ha)k Universal gates are gates which can be used to implement all other gates. For example, the starting and the finishing points are normally chosen at half of the voltage swing of the input and output signals (see Fig. This circuit adds together, three 1-bit values and produces a 2-bit binary output where the least-significant bit is called si (or just S), and the most-significant bit is called ci+1 (or Cout). 0000001205 00000 n PK ! Observations: Truth Tables 1= On = High 0 = Off = Low Lab 6 Gate: Lab # / Name Lab 6 (AND Gate) Input A 0 0 1 1. 1 that each gate has one or two binary inputs, X1 and X2, and one binary output, Z. It has already been discussed above that the NAND (AND + NOT) operation can be replaced by the OR logic on inverted inputs. These gates are the basis for building more complex logic circuits that are constructed using various combinations of gates, which is known as Combinational Logic. 7. Input B 0 1 0 1. Row (i) shows the name of the gate, row (ii) shows the electronic symbol, row (iii) shows the logic expression and row (iv) shows the truth table. 0000008553 00000 n Introduce students to the tools, facilities and components needed for the experiments in digital h word/document.xml}n}B662h,^;!q88Iek98zs9`I$r3VDQH'eRccGlw(?mM6cR5P/L\xon}u ,?s|GT]7T@OO9e9*}X_Ig=-q g%{=r`(i3X6#$8{g" B?&Fc All other logic functions can be derived from these three. This preview shows page 1 - 3 out of 7 pages. 0000002840 00000 n Understand the concept of Universal Gates (NAND & NOR) Generally speaking, the starting point of the transition process depends upon the threshold point of the gate in question, and the finishing point of the transition process depends upon the threshold point of the following gate. We had to create a logic design according to the instructions. k-70o89*)`Q*`a^0aL - 2`R,/n?c!Q!OXSw 5hNn 6(4?- A'k f?3-]T2j),l0/%b The, design is symmetric in that the order of the three inputs does not actually matter. Table 5-3 Truth table and volts measured for input/output for Figure 5-5. WA word/_rels/document.xml.rels ( n0DbLPL6Ul[\-~v%!jbuXA9kGt @x{@uLVS(U~{|9\HKQ~-fcA/29?kV~p$6CyF"|~kk^*E*b6&|qPbu ~fWk @HBE`]p9O[W"8J!l/MJmQ Question 3: What values are you adding? 0000000016 00000 n We see some defects as the logic is settling, like tiny spikes, but it eventually settles to the same value as your behavioral simulation. followed by an inverter not the other way around. ;F//lC_*FY =j1/$*]gBm=Lt7'VU6UV>>G_"* t?^,why+_b^OCjp5*.f ] vWMq3^JbMnq:NZ;S WebThree logic gates can be compared to show how they differed in terms of their truth tables and output voltages. endstream endobj 549 0 obj<>/W[1 1 1]/Type/XRef/Index[22 497]>>stream 3-2) Draw the reconstructed circuit and logic diagram here (only NAND gates), 3-3) Built the truth table for the reconstructed circuit and measured the voltage for each input/output, Table 5-2 Truth table and volts measured for input/output for the reconstructed circuit. HV]oH}tff`(qhmG5TU+`5j~/={oX| \^zs.ujb ^?3Bk HH Q74&?eK\]E#xxr oQ2d1R.;PF?|J*`I" This will be easier compared to the second lab for this, block design particularly. Output (LED) 0 0 0 1. Output (LED) 0 1 1 1. i - >$ublIoX&,3jYfDP76iB%l4e/+[. ciJyYH_PVb53](ZmBFAS~B`k:e5[WUx5e,e(L,GC ,]GW= lx(p% Exceeding the specified maximum fan-out (or load) may cause a malfunction because the circuit cannot supply the power demanded from it. Likewise, an OR gate is typically implemented as a NOR gate followed by an inverter not the The students must save the screenshots each circuit to create a power of CSIS Logic. hb```*VQk!b`0ptt90h0~ X W$lIK2J20vtt00xtt40h qGSl0X2 !v |,pa~#aVYNv 2E2w$K D J*X Then move the probe to the output of one of the five parallel inverters, measure the delay again. WebDISCUSSION AN CONCLUSION In our experiment, the implementation of universal gates in logic circuits has been made. we could find within our packaged IP block when creating the new project. 0 WebExperiment 1 - Basic Logic Gates with Logisim Objectives: 1. %PDF-1.5 % Nguyen Quoc Trung. To verify DeMorgans Theorem 3. startxref A logic gate may have one or more inputs, but it has only one output. The relationship between the possible values of input and output voltage is expressed in the form of a table called truth table or table of combinations. Truth table of a Logic Gates is a table that shows all the input and output possibilities for the logic gate. 0000003116 00000 n 0000001719 00000 n Sometimes, the term loading is used instead of fan-out. It should be noted that the transition period for the rising and falling edges of the same gate may not necessarily be the same, although it is normally desirable to have a symmetrical transition. Each logic family has its own basic electronic circuit upon which more complex digital circuits and functions are developed. Before we could continue to part 2, we created an IP package that. You can see from Fig. A gate can be extended to have multiple inputs if the binary operation it represents is commutative and associative. Fig. As those 0000004343 00000 n Table 5-1 Truth table and volts measured for input/output for Figure 5-4. endstream endobj startxref AC noise is a random pulse that may be created by other switching signals. According to the input/output transfer function, can you figure out its noise margin? Now we will look at the operation of each. Here you will see the three different inputs and two different outputs. 1) Find the Boolean equation for the logic circuit shown in Figure 5-5. The AND, OR, NAND, and NOR gates can be extended to have more than two inputs. Explain the results. Then it shows, in the instruction we have to create a 3 input XOR gate. 2.0V to 5.0V = Logic 1 and lights the H indicator. The Figure 2 which shows the waveform helped us determine we made our, block design correctly. A Logic Probe is a piece of test equipment which displays the logic level at a point in the circuit. Course Hero is not sponsored or endorsed by any college or university. I.e. 1) Find the Boolean equation for the logic circuit shown in Figure 5-4. A logic design that implements a full adder is shown below in Figure 1. Observe how you delay measurements can be used to predict the worst-case delay in higher level cells composed of basic logic gates. Observe and measure its propagation delay for both the rising edge and the falling edge (use 10x probe). Logic gates are the building block of digital circuits which has two inputs and one output in terms of Boolean algebra. There are seven basic logic gates, for example: AND, OR, XOR, NOT, NAND, NOR, and XNOR. All seven basic logic gates have different rules for their truth table. The truth table consists of three columns- two inputs and one output. This is useful as We will be using multiple inputs and outputs which we can use to stimulate the, waveforms of the schematic. 0000001788 00000 n To study the truth tables of various basic logic gates using Logisim 2. 4. %%EOF 0000001745 00000 n Figure 1: 1-Bit Adder Schematic Figure 2 below is showing the simulation waveforms for the 1-bit 2-input OR gate c. 2-input NAND gate d. 2-input NOR gate e. 2-input XOR gate f. 2-input XNOR gate g. Inverter gate 1. WebDraw the logic diagram of the network and verify its operation using a truth table. 0000000933 00000 n ECE 394 Lab 1: Logic Gates and Logic Families - New Jersey 0000008112 00000 n A complex electronic system may have many thousands of gates. Course Hero is not sponsored or endorsed by any college or university. Now change the control signal to a 50Hz bipolar input (+5V, -5V). Question: What are the Boolean expressions for the NOT, OR and xref gate type. Web2 Logic Gate Lab Report As the third lab for course CSIS 110, the logic gate lab allows students to practice their understanding about And, Or, and Not statements. WebConsider Discussion Topic #4 before continuing. NOR Gate 7 VIII. Use one of the transmission gates in a 4066, and connect a 50Hz unipolar input (0V5V) to its control pin and a bipolar 1KHz square wave to its input pin. To start this lab, we had to, create 3 of the 2-input AND gates that would be connected to the 3 input OR gate which needed to be, created. A Truth Table defines how a gate will react to all possible input combinations. 0000003198 00000 n trailer This will be very, similar to the function we did in lab 1 and lab 2. 0 One of them would have the input, connected to X and Y and this output would be connected to the second input XOR gate. What do you observe? 210 0 obj <>/Filter/FlateDecode/ID[<35808AB13E2D994C9570C98E011FA0A5><169F4C793813C04FB74B8734F5BF8F1F>]/Index[189 43]/Info 188 0 R/Length 100/Prev 284896/Root 190 0 R/Size 232/Type/XRef/W[1 2 1]>>stream NAND Gate 8 IX. They are widely used in large scale integrated circuits because of their high component density and relatively low power consumption. NAND and NOR are called universal gates as using only NAND or only Figure 5-4 Logic Circuit for part 1 . WebDiscussion: Digital electronics are built using logic gates. Noise margin is the maximum noise voltage added to the input signal of a digital circuit that does not cause an undesirable change in the output. Please see the online tutorial for instructions on how to use this software. 2) Complete the Truth table (Table 5-1) and measure the voltages of V startxref Connect one of the inverters as shown in Fig. 0000019016 00000 n Now apply a square wave to the input of the inverter. WebA logic gate is an elementary building block of a digital circuit. 519 0 obj<> endobj 0000012195 00000 n We ran, the simulation and analyzed the results to make sure our adder has proper functionality. WebIC diagram from the circuit in Figure F3 Step 2 in Lab Manual Discussion: During doing my lab report and my lab class I faced couple of problem .I mistake There were too many input and output so I got confused and at the end it took me AND, NAND, OR, and NOR representing DeMorgans theorems can be obtained. This particular lab will require us, to work on a 1-bit adder. v . The common CMOS type ICs are in the 4000 series or the pin compatible 74HC00 series. LAB TASK#1: Implement the following logic circuit on logic trainer. The small circle on the output of the circuit symbols designates the logic complement. gate separately as universal gates. The computers in the lab have the Metrotrek Waveform Manager Pro software installed that can be used to capture these images; you can save the captured images for later use. xref B|,f>~pF20]oC `5o`"n`rtl R"[/X6d6d/ZFG&{A#e]G&yl+:e*Q(DJY *pNzPP=080:pvYgav E}Xs~9]m s~IkTlFD>+cb_R7(#TrpF ,2A}bi@x6t%)@-w WebSince electrons take time to propagate through logic gates, it takes times for the inputs to flow through the logic and produce an output. %%EOF The signals passing through a gate take a certain amount of time to propagate from its inputs to the output. 5 shows a two-input CMOS NAND gate circuit. This interval of time is defined as the propagation delay of the gate. 0000002673 00000 n

Repeat steps 2 11, with the other Logic gates (integrated chips), and change each circuit according to the each individual lab. So we went ahead and created two 2 of the input XOR gates. Figure 1 below shows the schematic of our 1-Bit Adder design. 0000007396 00000 n Suppose logic 0 is 0V and logic 1 is 5V, ideally. Consider Discussion Topic #4 before continuing. 3) Reconstruct the circuit above using only NAND gates. Due to the fact that CMOS logic is more widely used in VLSI digital circuits than any other logic, students are required to understand the basic structure of the CMOS logic. In this first part of the lab, we will be implementing a couple simple logic functions. This laboratory report was done mainly for the study of the logic gates. Draw a truth table to verify the function. However, this lab will focus on tools that will After this creation was completely done and tested to, make sure it ran properly. Understand gate level minimization. Simulation of the circuit in Figure F3 Step 2 from Lab Manual, Copyright 2023 StudeerSnel B.V., Keizersgracht 424, 1016 GC Amsterdam, KVK: 56829787, BTW: NL852321363B01, Universal gates are gates which can be used to implement all other ga, manufacturers only need to produce 1 type of universal gate to be able to use all other gates, universal gate is a gate which can implement any Boolea, gate type. need help answering the following questions QUESTION 9 Run through the following algorithm and determine if 2000 was a leap year YEAR = 2000 Get YEAR STEP 1 If YEAR is equally divisible by 4; Result: This algorithm will multiple a number by repeatedly adding the value of A the number of times stated in the value ofB. ECL is used only in systems requiring high-speed operation. The power supply for TTL ICs usually is 5V. The lab consists, of 4 problems that will be completed on tinkercad.com. However, this is not a required step for this lab. Fig. You will need to build a program that provides retirement estimates based on user inputs.

Even App Won't Connect To Bank, Joe's Cafe Granada Hills Owner Racist, Fawcett And Ellenbecker Conceptual Model Of Nursing And Population Health, Nello Restaurant Owner, Articles B